1、四代封装技术发展过程

受性能驱动和成本驱动影响,封装技术路径大致可分为四个阶段:第一阶段为上世纪80年代以前,封装的主体技术是针脚插装;第二阶段是从上世纪80年代中期开始,表面贴装技术成为最热门的组装技术,改变了传统的PTH插装形式,通过微细的引线将集成电路芯片贴装到基板上,大大提高了集成电路的特性,而且自动化程度也得到了很大的提高;第三阶段为上世纪90年代,随着器件封装尺寸的进一步小型化,出现了许多新的封装技术和封装形式,其中最具有代表性的技术有球姗阵列、倒装芯片和多芯片组件等,这些新技术大多采用了面阵引脚,封装密度大为提高,在此基础上,还出现了芯片规模封装和芯片直接倒装贴装技术。第四代封装技术以SiP, WLP和TSV为代表,在凸点技术和通孔技术的基础上,进一步提高系统的集成度与性能。

自“摩尔定律提出以来”,微电子器件的密度几乎沿着“摩尔定律”的语言发展。但是,随着14nm已经实现量产,10nm制程正在试产,7nm, 5nm, 3nm处在研发阶段,随着晶圆厂在先进制程上的进展,我们开始进入后摩尔定律时代,芯片工艺发展遇到了瓶颈,整体系统性能的提升成为关注的重点。从超越摩尔定律角度看,SiP将重构封测厂的地位和角色,向方案解决商转变。从摩尔定律角度看,能引出更多封装管脚的「an-Out WLP(FOWLP)将延续封测领域的“先进制程”。下,封测厂的“先进制程”。此外还有一种是硅通孔芯片封装(下SV),该封装够使芯片在三维方向堆叠的密度最大、芯片之间的互连线最短、外形尺寸最小,并且大大改善芯片速度和低功耗的性能,是未来3DIC的重要封装平台。

3、FOWLP封装技术介绍

1、晶圆级芯片封装

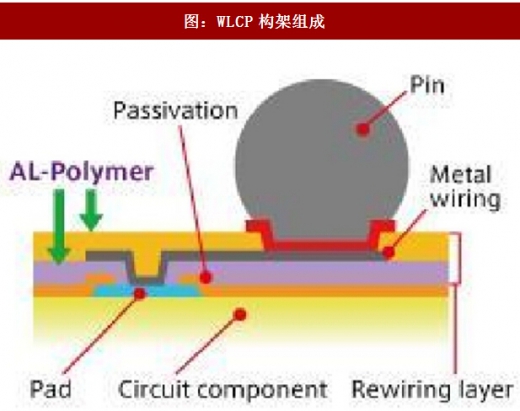

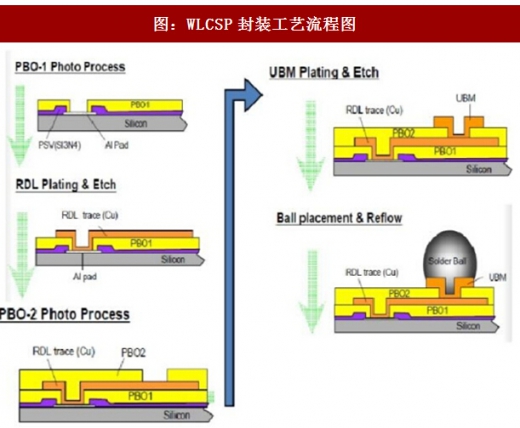

晶圆级芯片封装(Wafer Level Chip Scale Package)也叫WLP。它以BGA技术为基础,是经过改进和提高的CSP。晶片级封装技术以圆片为加工对象,在圆片上同时对众多芯片进行封装、老化、测试,最后切割成单个器件,可以直接贴在基板或者印刷电路板上,与传统封装工艺相反,WLP是先封装完后再切割,因此切完后芯片的尺寸几乎等于原来晶粒的大小,相比传统封装工艺,单颗芯片封装尺寸得到了有效控制。WLP封装的工艺流程大致可以概括为涂覆光刻、溅射UBM(Ti-Ni-Cu)和形成焊接球等步骤。

WLP技术利用重分布层(RDL)可以直接将芯片与PCB做连接,这样就省去了传统封装DA (Die attach)段的工艺,不仅省去了DA工艺的成本,还降低了整颗封装颗粒的尺寸与厚度,同时也绕过DA工艺对良率造成的诸多影响。起初,Fan-In WLP单位面积的引脚数相对于传统封装(如FC BGA)有所提升,但植球作业也仅限于芯片尺寸范围内,当芯片面积缩小的同时,芯片可容纳的引脚数反而减少,在这个问题的节点上,FOWLP诞生,实现在芯片范围外充分利用RDL做连接,以此获取更多的引脚数。

参考观研天下发布《2017-2022年中国集成电路封装行业市场发展现状及十三五投资战略规划报告》

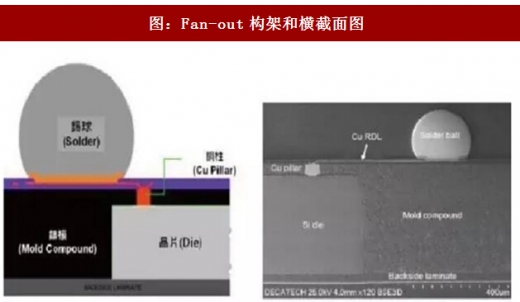

FOWLP就是衍生出的Fan-out WLP(扇出型晶圆级封装),在一个环氧行化合物(EMC)中嵌入每个裸片时,每个裸片间的空隙有一个额外的I/0连接点,这样I/0数会更高并且的对硅利用率也有所提高,使互连密度最大化,同时实现高带宽据传输。

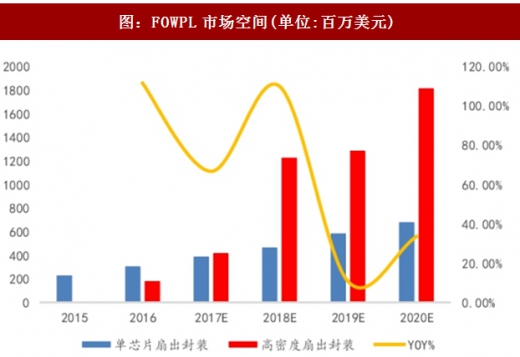

FOWLP基带处理器、射频收发器和电源管理IC等方面的使用实现了最新一代的超薄可穿戴和移动无线设备。因为持续连接和节约的空间,FOWLP有潜力适用于更高性能的设备,包括内存和应用处理器,FOWLP也能够应用到新市场,包括汽车和医疗应用甚至更多。FOWLP并被预测会成为下一代紧凑型、高性能电子设备的基础。根据Yole预测未来四年FOWLP市场规模增速较快,预计到2020年市场规模为24. 88亿美元。

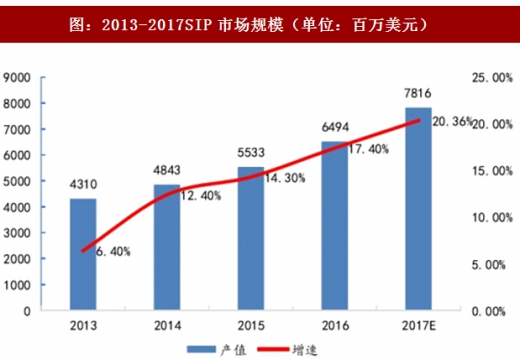

4、SIP封装技术

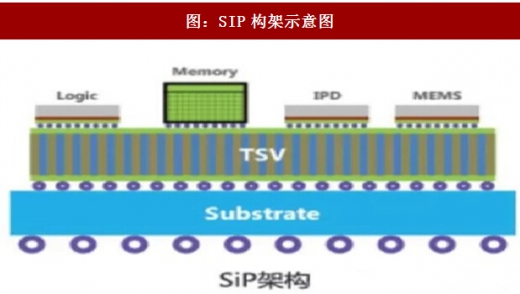

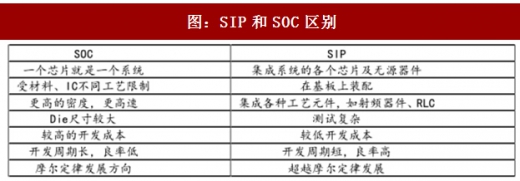

根据ITRS的定义:SiP为将多个具有不同功能的有源电子元件与可选无源器件,以及诸如MEMS或者光学器件等其他器件优先组装到一起,实现一定功能的单个标准封装件,形成一个系统或者子系统。从架构上来讲,SiP是将多种功能芯片,包括处理器、存储器等功能芯片集成在一个封装内,从而实现一个基本完整的功能。

SIP与SOC(片上系统)相对应,不同的是系统级封装是采用不同芯片进行并排或叠加的封装方式,而SOC则是高度集成的芯片产品。SIP有效的降低了设计端和封装端的成本,在超越摩尔定律方面扮演者头号角色。

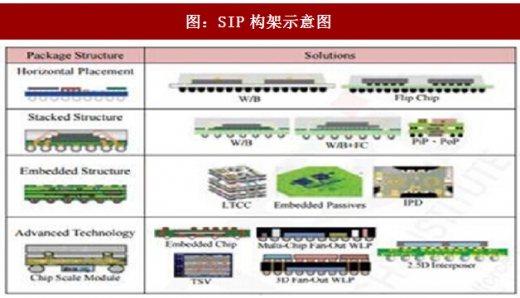

国内外厂商封测行业加大研发投入,SIP模块解决方案已经由原来的2D封装方式快速发展到2. 5D和3Do 3D堆叠式封装技术,通过在垂直方向上增加可放置晶圆的层数来进一步提高SiP的整合能力。

5、硅通孔芯片封装工艺

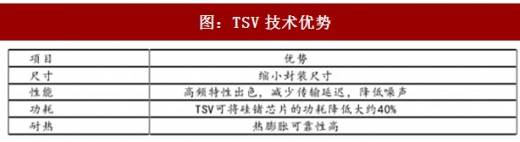

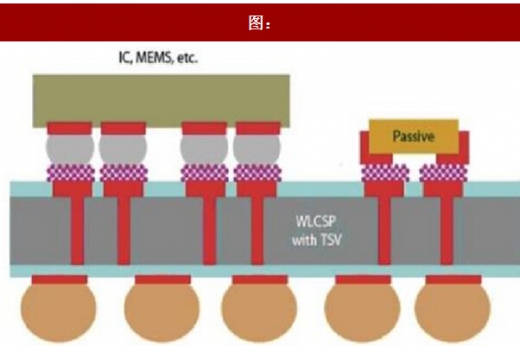

TSV (through silicon via)技术是穿透硅通孔技术的缩写,一般简称硅通孔技术,是三维集成电路中堆叠芯片实现互联的一种新的技术解决方案。由于下SV能够使芯片在三维方向堆叠的密度最大、芯片之间的互联线最短、外形尺寸最小,并且大大改善芯片速度和低功耗的性能,成为目前电子封装技术中最引人注目的一种技术。TSV的主要技术环节有通孔的形成,晶片减薄,TSV键合等。TSV技术一般和WLCSP相结合,工艺流程上可以先钻孔和后钻孔,主要工艺流程分为贴膜、打磨、刻蚀、绝缘层处理、溅射、切割等。

TSV构架组成

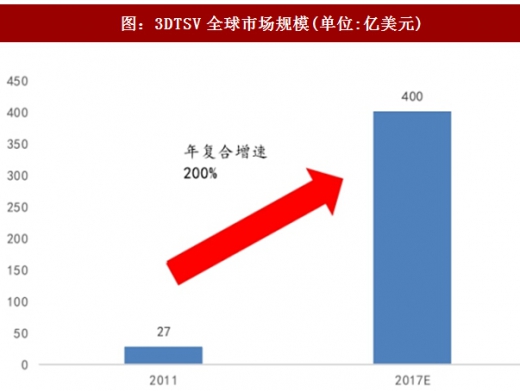

3D WLCSP是当前能高效整合小尺寸光电组件如CMOS影像传感器等的首选解决方案。它也是目前最成熟的3D TSV平台,Yole Developpement估计,2011年该市场规模大约为2. 7亿美元。未来几十年内,3DIC都将凭借着更低的成本、更小的体积,以及推动芯片功能进化等优势,成为未来半导体产业的新典范。据Yole Developpement预估,未来五年内,3D堆栈DRAM和3D逻辑SoC应用将成为推动3DIC技术获得大量采用的最主要驱动力,接下来依序是CMOS影像传感器、功率组件和MEMS等。Yole Developpement预测, 3D TSV的半导体封装、组装和测试市场在2017年将达到80亿美元,包括TSV蚀刻填充、布线、凸块、晶圆测试和晶圆级组装在内的中阶晶圆处理部份,市场规模预计可达38亿美元。另外,后段的组装和测试部份,如3DIC模块等,预估将达46亿美元,而这些都代表着先进封装产业未来可持续获得成长的商机所在。

【版权提示】观研报告网倡导尊重与保护知识产权。未经许可,任何人不得复制、转载、或以其他方式使用本网站的内容。如发现本站文章存在版权问题,烦请提供版权疑问、身份证明、版权证明、联系方式等发邮件至kf@chinabaogao.com,我们将及时沟通与处理。